Eagle CADのベタパターン設定の方法を記載します。

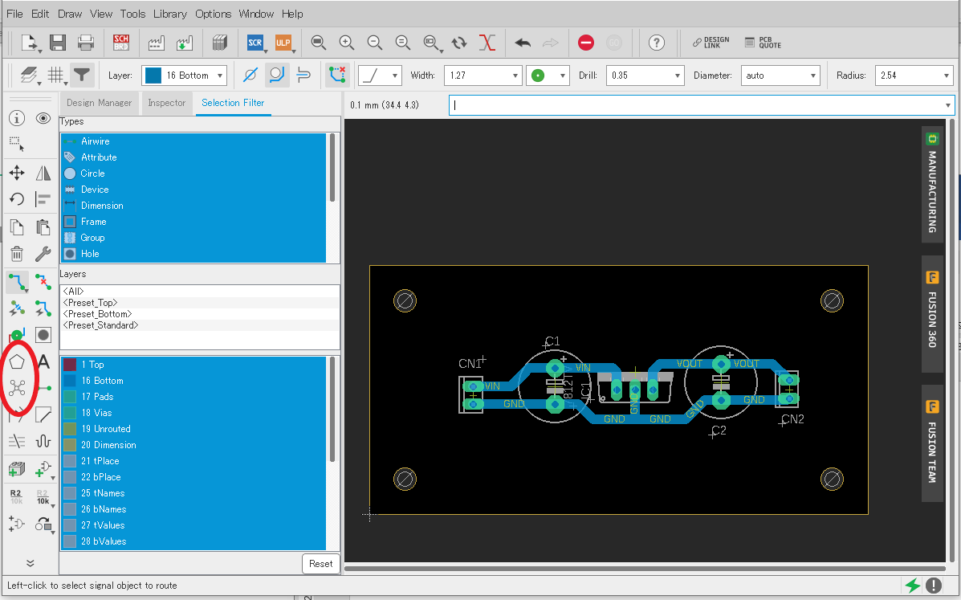

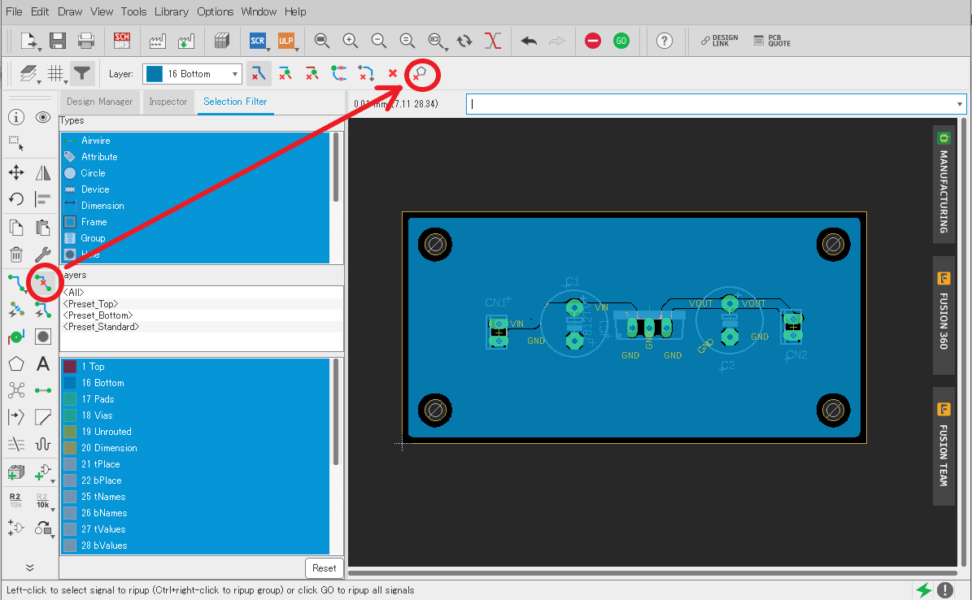

使うボタンは赤〇で囲んだ「Polygon」と「Ratsnest」です。

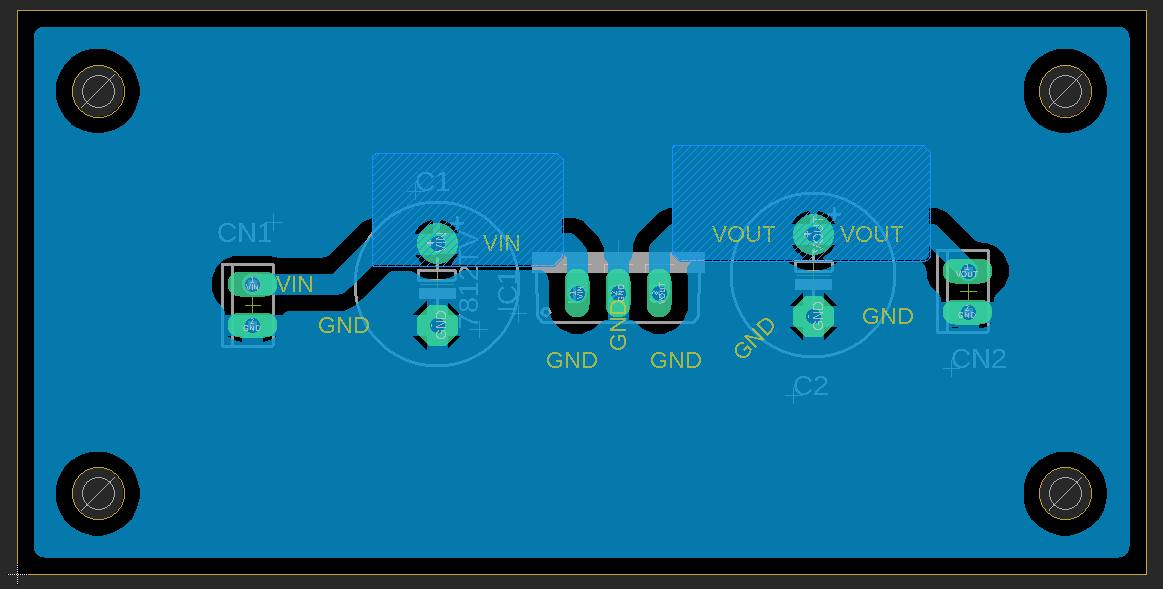

サンプルボート図は下図のような、TO220三端子レギュレータの入力と出力に電解コンデンサとコネクタを接続し、Bottom側に簡単な配線をしただけの基板です。

図 1 開始のボード図

図 1 開始のボード図

目次

1 ベタグランド(ベタアース)の作成

まずはベタアースの作成を行います。

「Polygon」を使って基板の外周を囲ってみましょう。下記の画面がでるので、まずは[GND]と入力します。

図 2 信号名の入力

図 3 ポリゴンの設定

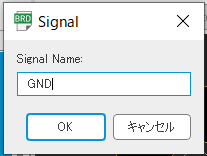

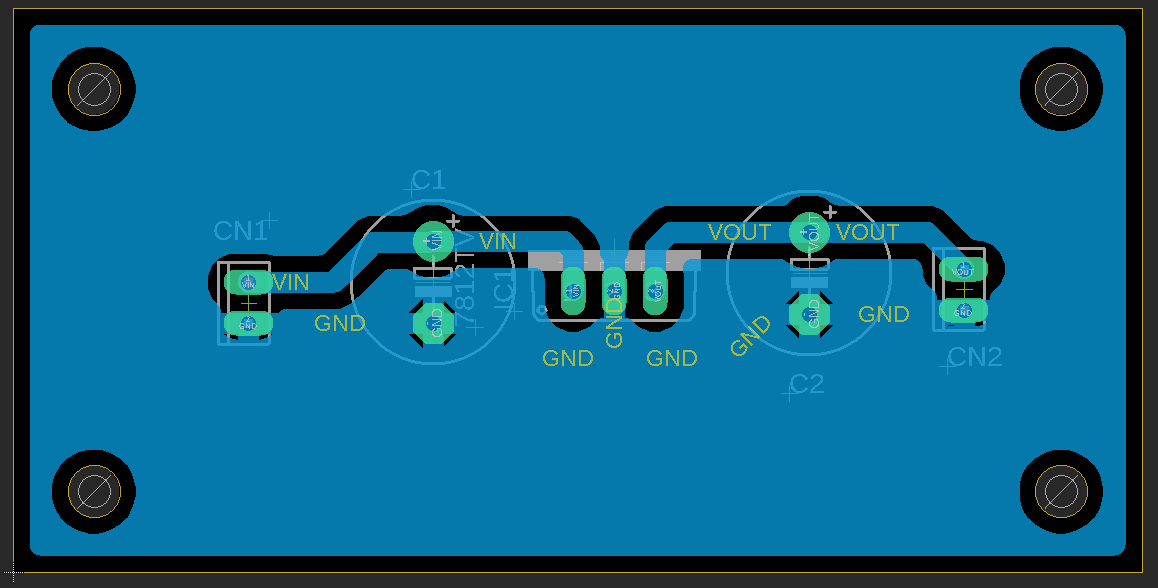

そして、「Ratsnest」ボタンを押すとベタグランドが出来上がります。

図 4 ベタグランドの完成1

VOUTとVINの配線がGNDに近づきすぎて不安な場合は、クリアランスを大きくとることができます。初期のクリアランスは設計ルール(DRC)で設定した値です。

パターン間のクリアランス、デフォルトでは6mil(約0.15mm)が適用されます。

すこしクリアランスを取りましょう。まずは一旦ベタバターンを解除します。

下の図のように「Ripup」→「All visible polygons」を押すと図 3にもどります。

図 5 ベタパターンの解除

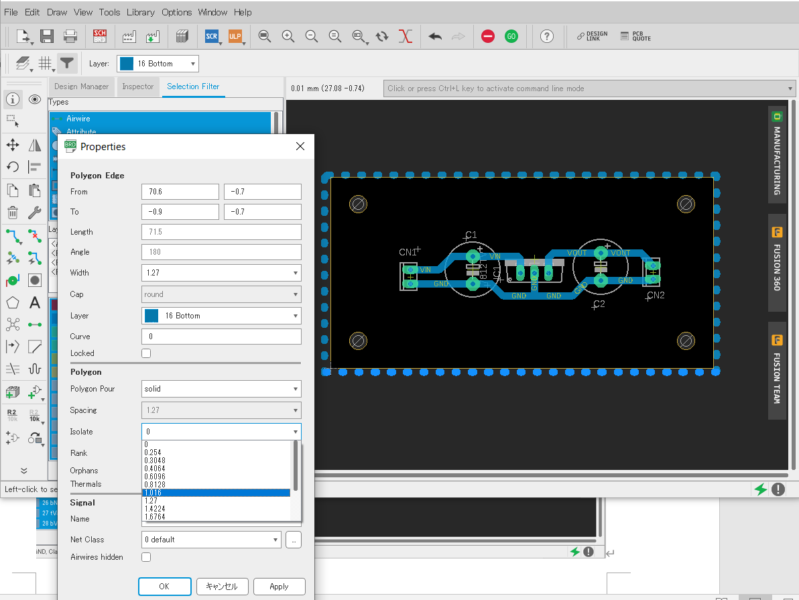

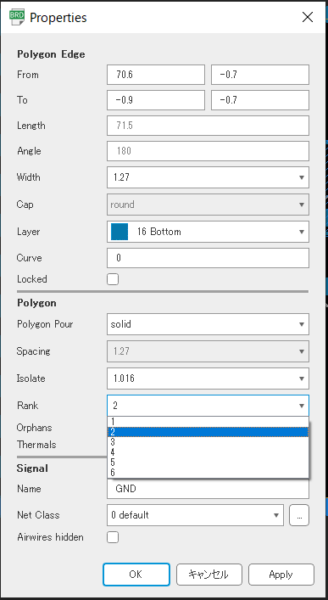

図 3の状態から、ポリゴンのインフォメーションを表示させると図 6の画面が現れます。

その時に[Isolate]の値を初期値の[0]から例えば[1.016]に変更し[OK]ボタンを押し、「Ratsnest」でベタパターンを再生成すると、図 7のように指定したクリアランスのベタパターンが出来上がります。

図 6 ポリゴンのインフォメーション

図 7 指定したクリアランスのベタパターン

2 ポリゴン in ポリゴン

さて、パターンを太くしたいのはGNDだけではありません、できればVINとかVOUTのパターンも太く引きたいですよね。この時はそれぞれの配線に更にポリゴンを付加します。

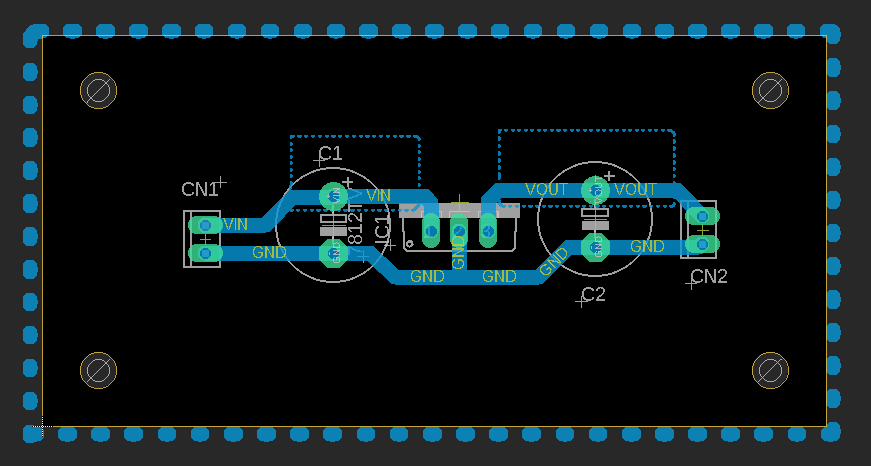

では早速やってみましょう。図 3の状態に戻って、ポリゴンを追加します。

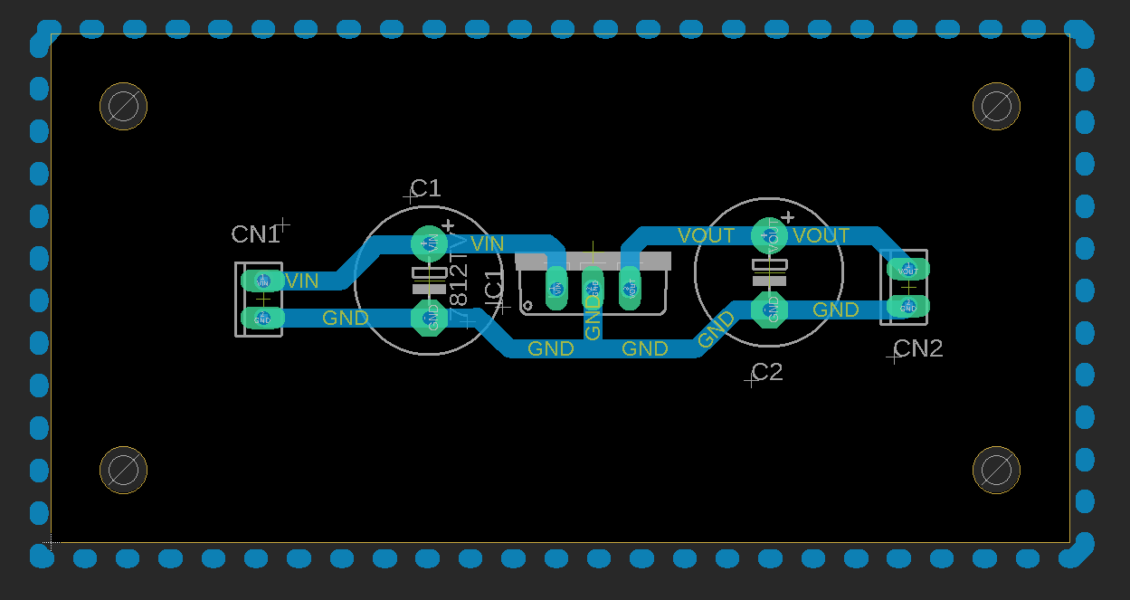

VINとVOUTにそれぞれ、細い線でポリゴンを作成してみました。ポリゴンの中に(同一ランクの)ポリゴンを挿入したので、ハッチングが入ったものと思われます。

図 8 ポリゴンの追加

この状態で「Ratsnest」を押します。

すると、図 9の様に後で作成したベタパターンとGNDのパターンが短絡しています。

これは困りました。

図 9 ベタパターン作成でパターン短絡

この対策はポリゴンのRank(優先順位)付けで解決できます。

外側のポリゴン(この場合GNDパターン)のRankを下げます。

外側のポリゴンのRankをデフォルトの[1]→[2]に下げましょう。

この設定はポリゴンのインフォメーションの画面で設定できます。

図 10 ポリゴンのランク変更

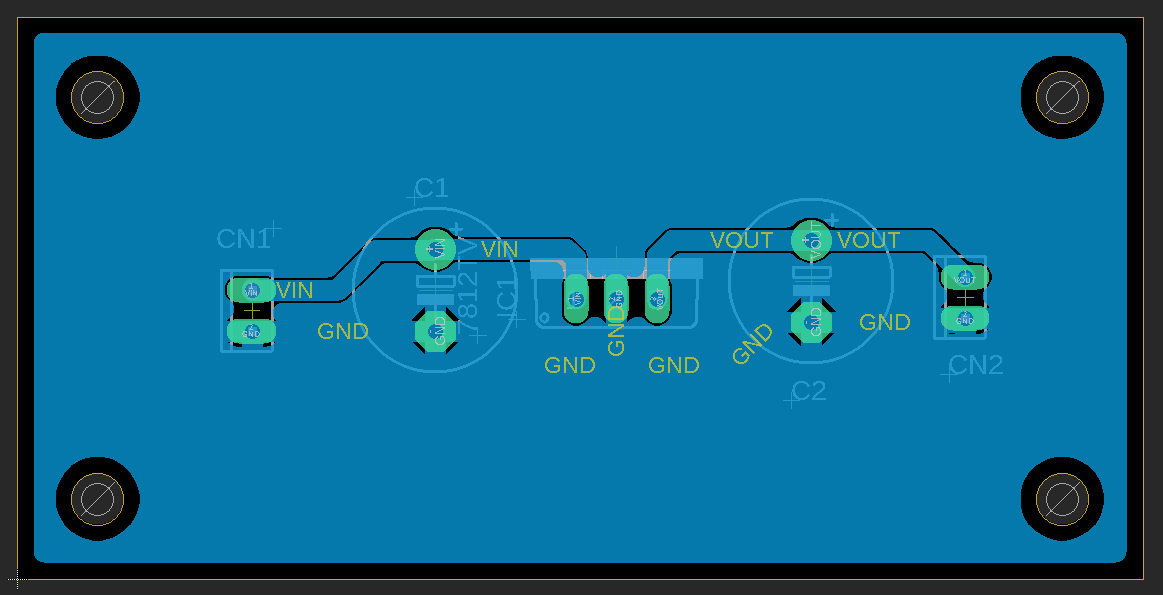

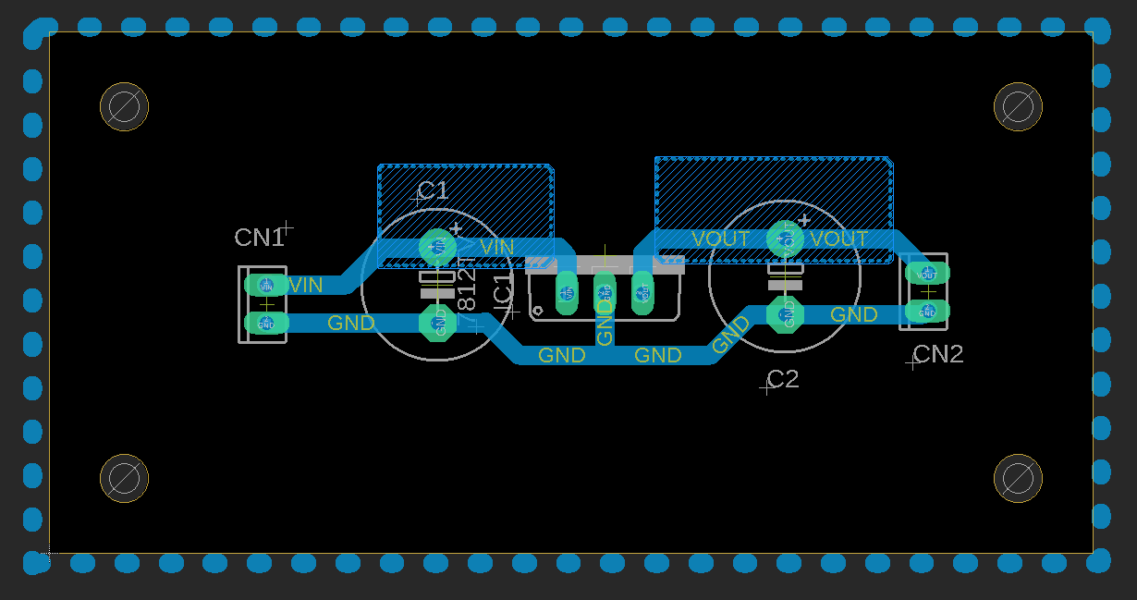

そうすると、先ほどまであったハッチングが図 11のように消えます。

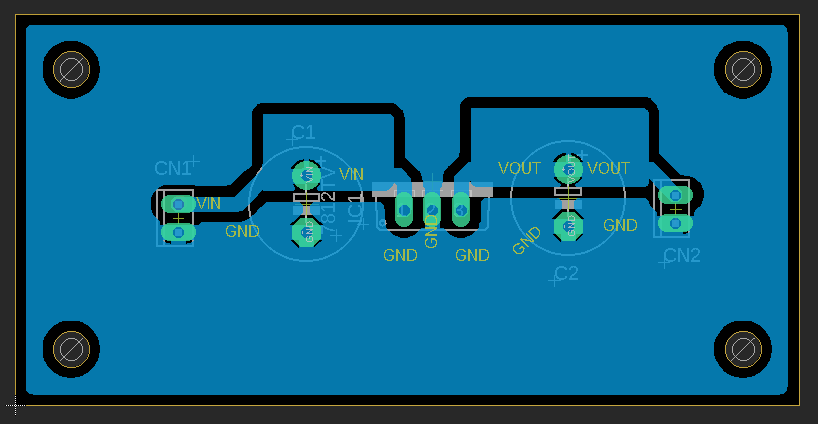

この状態で「Ratsnest」を押すと、図 12のように、期待通りのベタパターンが出来上がります。

図 11 内側のポリゴンのランク変更

図 12 内側のランク変更後のベタパターン

尚、図10で[Width]の設定がありますが、これは、ポリゴンの囲い線の太さを決めるだけではなく、塗りつぶし領域で塗りつぶされる領域の最小の太さも規定しています。GNDのベタパターンの場合は[Width]を細くすると、細い線が狭い隙間まで入り込んで、あまり見てくれが良くありませんので、少し太めの線(ここでは1.27mm)で囲う方が良いです。

以上 ベタパータンの作成方法の解説でした。